基础参数

|

|

模块 |

简要说明 |

|

X20 CPUs |

X20CP1381 |

X20 CPU,集成I/O,x86-200,128 MB DDR3 RAM,16 kB FRAM,1 GB板载闪存,1个X20接口模块插入槽,2个USB接口,1个RS232接口,1个CAN总线接口,1个POWERLINK接口,1个10/100BASE-T以太网接口,14个数字输入,24 VDC,汇,4个数字输入,2 µs,24 VDC,汇,4个数字输出,24 VDC,0.5 A,源,4个数字输出,2 µs,24 VDC,0.2 A,4个数字输入/输出,24 VDC,0.5 A,2个模拟输入±10 V或0至20 mA / 4至20 mA,1个PT1000代替模拟输入,包括电源模块,3个接线板X20TB1F,槽盖和X20端盖板X20AC0SR1(右)包括 |

X20CP1382 |

X20 CPU,集成I/O,x86-400,256 MB DDR3 RAM,32 kB FRAM,2 GB板载闪存,1个X20接口模块插入槽,2个USB接口,1个RS232接口,1个CAN总线接口,1个POWERLINK接口,1个10/100BASE-T以太网接口,14个数字输入,24 VDC,汇入,4个数字输入,2 µs,24 VDC,汇出,4个数字输出,24 VDC,0。5 A,源,4个数字输出,2 µs,24 VDC,0.2 A,4个数字输入/输出,24 VDC,0.5 A,2个模拟输入±10 V或0至20 mA / 4至20 mA,1个PT1000代替模拟输入,包括电源模块,3个接线板X20TB1F,槽盖和X20端盖板X20AC0SR1(右)包括 |

模块 |

数量 |

简要说明 |

- |

1 |

Interface module slot cover |

X20AC0SR1 |

1 |

X20 end cover plate (right) |

X20TB1F |

3 |

X20 terminal block, 16-pin, 24 VDC keyed |

系统要求:

建议使用以下最低版本,以便通常能够使用所有功能。

•AS 4.1.4.96

•适用于所有其他变体的AR D4.09

接线:

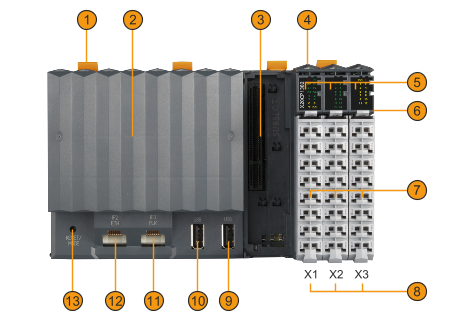

图: X20CP1382的操作元件

顶帽导轨锁扣 |

2 |

集成闪存驱动器 |

|

3 |

用于接口模块的插槽 |

4 |

用于CAN总线终端电阻的开关 |

5 |

LED状态指示灯 |

6 |

IF6 - X2X链接 |

7 |

用于连接。电源,I/O通道,IF1 - RS232,IF7 - CAN总线 |

8 |

3个集成I/O插槽。X1、X2和X3 |

9 |

IF5 - USB |

10 |

IF4 - USB |

11 |

IF3 - POWERLINK |

12 |

IF2 - 以太网 |

13 |

用于复位和操作模式的按钮 |

- |

- |

Slot X1(含CAN口) 接线时注意CAN high接CAN high,CAN low接CAN low

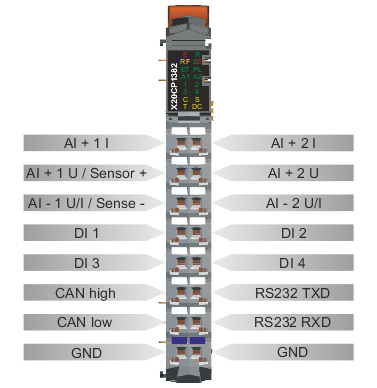

图: 集成X1 I/O插槽的引脚分布

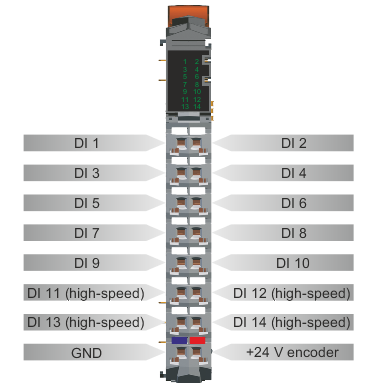

为了防止串扰,高速数字输入的每条信号线应单独屏蔽。最大的电缆长度为20米。

图: 集成的X2 I/O插槽的引脚分布

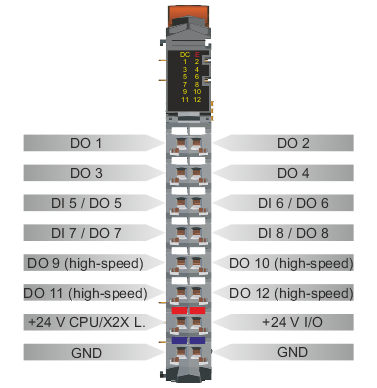

为了确保数字混合通道(DI 5 / DO 5 至 DI 8 / DO 8) 的正常运行,必须遵守 紧凑型CPU的电源概念一节中的说明 。

为防止串扰,高速数字输出的每条信号线应单独屏蔽。最大的电缆长度为20米。

图: 集成的X3 I/O插槽的引脚分布

LED灯状态指示

图 |

LED |

颜色 |

状态 |

描述 |

|

C |

黄色 |

ON |

CPU通过CAN总线接口发送或接收数据 |

T |

黄色 |

ON |

CPU集成的终端电阻处于打开状态。 |